MADR-011034

Rev. V1

#### **Features**

- -10 V to -25 V Back Bias

- 25 mA Sinking Current

- · 20 mA Sourcing Current

- Propagation Delay <130 ns Driving 100 pF Capacitive Load

- Quiescent Currents <1 mA</li>

- TTL Logic Control

- Internal Active Pull Down for All Logic Controls

- Internal Power Sequencer Eliminates External Power Sequencing

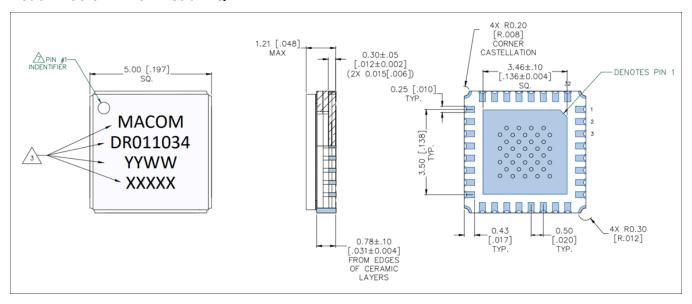

- 5 mm 32-Lead Ceramic QFN Package

- · Hermetically Sealed

- Upon Request Available as a Fully Screened Device (Class K & Class H)

- RoHS\* Compliant

### **Applications**

- Aerospace & Defense

- ISM

### **Description**

The MADR-011034 switch driver is designed to work with MACOM's HMIC 20 W CW SPDT PIN diode switches. This driver has complementary outputs which can provide up to 25 mA sinking and 20 mA sourcing bias current to a SPDT PIN diode switch. An all-off RF state can be achieved with the EN pin of this driver. An extra control C2 with driver select DS are provided to allow two drivers working together to drive a SP3T or SP4T switch.

The back bias voltage can be selected to be any voltage between -10 V and -25 V. This switch driver can be easily controlled by standard TTL logic. With low quiescent current, this driver has a typical delay of <130 ns when driving a 100 pF capacitive load.

This driver is packaged in a lead-free 5 mm 32-lead CQFN package and is available in tape and reel packaging for high volume applications.

### **Ordering Information**

| Part Number     | Package            |

|-----------------|--------------------|

| MADR-011034     | 49 pc. waffle pack |

| MADR-011034-SMB | Sample Board       |

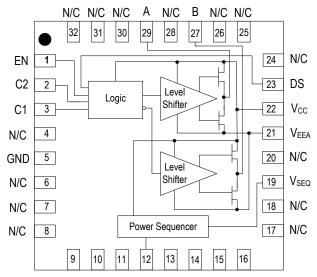

#### **Functional Schematic**

N/C N/C N/C VEEB N/C N/C N/C N/C

### **Pin Configuration**

| Pin#                                                                                      | Pin<br>Name         | Description of Function         |

|-------------------------------------------------------------------------------------------|---------------------|---------------------------------|

| 1                                                                                         | EN                  | Enable                          |

| 2                                                                                         | C2                  | Logic Control Input             |

| 3                                                                                         | C1                  | Logic Control Input             |

| 5                                                                                         | GND                 | Ground                          |

| 12                                                                                        | V <sub>EEB</sub>    | Negative Bias for Sequencer Die |

| 19                                                                                        | $V_{SEQ}$           | Power Sequencer Die Output      |

| 21                                                                                        | V <sub>EEA</sub>    | Negative Bias for Driver Die    |

| 22                                                                                        | V <sub>CC</sub>     | Positive Bias                   |

| 23                                                                                        | DS                  | Driver Select                   |

| 27                                                                                        | В                   | Inverted Driver Output          |

| 29                                                                                        | Α                   | Non-inverted Driver Output      |

| 4, 6, 7, 8, 9,<br>10, 11, 13, 14,<br>15, 16, 17, 18,<br>20, 24, 25, 26,<br>28, 30, 31, 32 | N/C <sup>2</sup>    | No Connection                   |

| 33                                                                                        | Paddle <sup>3</sup> | Ground                          |

- 2. N/C pins should be left open.

- MACOM recommends connecting the exposed pad centered on the package bottom to RF, DC and thermal ground.

<sup>\*</sup> Restrictions on Hazardous Substances, compliant to current RoHS EU directive.

MADR-011034

## Recommended Operating Conditions<sup>4</sup>

| Parameter                                         | Test Conditions        | Units | Min.       | Тур.                   | Max.                   |

|---------------------------------------------------|------------------------|-------|------------|------------------------|------------------------|

| V <sub>CC</sub>                                   | _                      | V     | 4.5        | 5.0                    | 5.5                    |

| $V_{\text{EEA}}$ and $V_{\text{EEB}}$             | _                      | V     | -25        | _                      | -10                    |

| C1, C2, EN, DS                                    | Logic "0"<br>Logic "1" | V     | 0.0<br>2.0 | 0.0<br>V <sub>CC</sub> | 0.8<br>V <sub>CC</sub> |

| I <sub>SINK</sub> , Sinking Current per Output    | _                      | mA    | _          | _                      | 25                     |

| I <sub>SOURCE</sub> , Sourcing Current per Output | _                      | mA    |            | _                      | 20                     |

| Total Capacitive load per Output (Operating)      | _                      | pF    | _          | _                      | 100                    |

| Rise / Fall Time of $V_{CC}$ and $V_{EEB}$        | _                      | μs    | 1          | _                      | _                      |

| Operating Temperature                             | _                      | °C    | -40        | +25                    | +85                    |

<sup>4.</sup> Negative bias should be applied to V<sub>EEB</sub> (pin 12). The sequencer output V<sub>SEQ</sub> should be connected to the driver die negative bias V<sub>EEA</sub>. A 47 pF shunt capacitor shall be placed close to pin 21 (V<sub>EEA</sub>).

## **Absolute Maximum Ratings**<sup>5,6</sup>

| Parameter                               | Absolute Maximum                                                                    |

|-----------------------------------------|-------------------------------------------------------------------------------------|

| V <sub>CC</sub>                         | -0.5 V ≤ V <sub>CC</sub> ≤ +7 V                                                     |

| V <sub>EEA</sub> , V <sub>EEB</sub>     | $-30 \text{ V} \le \text{V}_{\text{EEA}}, \text{V}_{\text{EEB}} \le +0.5 \text{ V}$ |

| C1, C2, EN, DS                          | -0.5 V ≤ V <sub>CC</sub> ≤ +7 V                                                     |

| Sinking Current per Output              | 35 mA                                                                               |

| Sourcing Current per Output             | 30 mA                                                                               |

| Capacitive Load per Output <sup>7</sup> | 125 pF                                                                              |

| Operating Temperature                   | -40°C to +110°C                                                                     |

| Storage Temperature                     | -55°C to +150°C                                                                     |

Exceeding any one or combination of these limits may cause permanent damage to this device.

## Logic Truth Table<sup>8,9</sup>

|    | Inp | Out | puts |   |   |

|----|-----|-----|------|---|---|

| EN | DS  | C2  | C1   | Α | В |

| 1  | Х   | Х   | Х    | Н | Н |

| 0  | 0   | 0   | 0    | L | Н |

| 0  | 0   | 0   | 1    | Н | L |

| 0  | 0   | 1   | 0    | Н | Н |

| 0  | 0   | 1   | 1    | Н | Н |

| 0  | 1   | 0   | 0    | Н | Н |

| 0  | 1   | 0   | 1    | Н | Н |

| 0  | 1   | 1   | 0    | L | Н |

| 0  | 1   | 1   | 1    | Н | L |

<sup>8.</sup> The actual output low voltage can be calculated by:

MACOM does not recommend sustained operation near these survivability limits.

Capacitive load above 125 pF can cause peak current exceeding power limit for the MOSFETs in the output buffer.

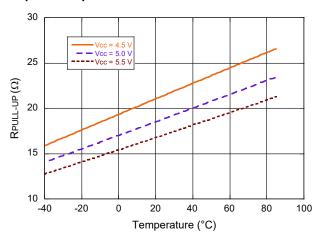

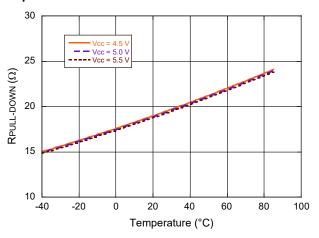

$V_{OL} = V_{EEB} + I_{SINK} x R_{Pull-Down}$ . The actual output high voltage can be calculated by:  $V_{OH} = V_{CC} - I_{SOURCE} \times R_{Pull-Up}$ .

MADR-011034

## Electrical Specifications: $T_A = 25$ °C, $V_{CC} = 5$ V, $V_{EEB} = -25$ V

| Parameter                                                                                                                    | Test Conditions                                                                                      | Units | Min. | Тур.                 | Max. |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------|------|----------------------|------|

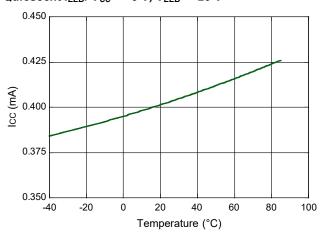

| V <sub>CC</sub> Quiescent Current                                                                                            | C1 = 5 V, C2 = DS = EN = 0 V                                                                         | mA    | _    | 0.4                  | 0.5  |

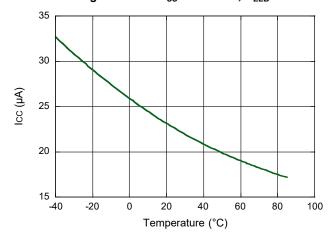

| V <sub>EEB</sub> Quiescent Current                                                                                           | C1 = 5 V, C2 = DS = EN = 0 V                                                                         | mA    | _    | 0.4                  | 0.5  |

| Control Input Leakage Current <sup>10</sup>                                                                                  | Control = 5 V                                                                                        | μA    | _    | 20                   | 25   |

| R <sub>PULL-UP</sub> , Output Pull-up On Resistance                                                                          | 20 mA Load                                                                                           | Ω     | _    | 19                   | 25   |

| R <sub>PULL-DOWN</sub> , Output Pull-down On Resistance                                                                      | 25 mA Load                                                                                           | Ω     | _    | 19                   | 25   |

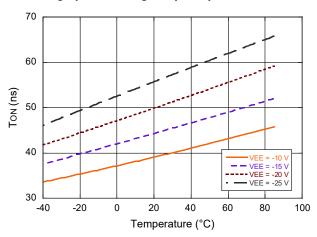

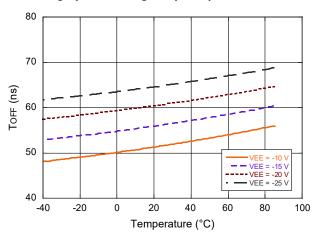

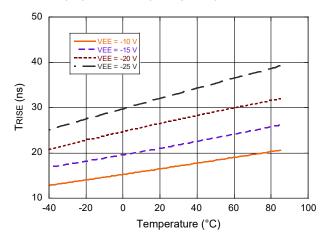

| Switching Speed Driving 100 pF Capacitors <sup>11</sup> T <sub>ON</sub> T <sub>OFF</sub> T <sub>RISE</sub> T <sub>FALL</sub> | 50% control to 90% Voltage<br>50% control to 10% Voltage<br>10% to 90% Voltage<br>90% to 10% Voltage | ns    | _    | 56<br>68<br>31<br>29 | _    |

| Switching Speed Driving MASW-002103 Switch $^{12}$ $T_{\rm ON}$ $T_{\rm OFF}$ $T_{\rm RISE}$ $T_{\rm FALL}$                  | 50% control to 90% Voltage<br>50% control to 10% Voltage<br>10% to 90% Voltage<br>90% to 10% Voltage | ns    | _    | 75<br>69<br>22<br>50 | _    |

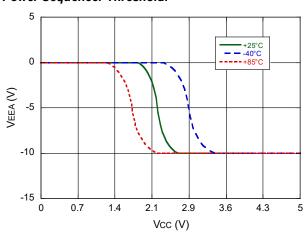

| Power Sequencer Threshold Voltage                                                                                            | Note 13                                                                                              | V     | _    | 2.5                  | _    |

| Power Sequencer Power On Time                                                                                                | Note 14                                                                                              | μs    | _    | 25                   | _    |

| Driver Die Power Up Time                                                                                                     | Note 15                                                                                              | μs    | _    | 1                    | _    |

| Driver Die Power Down Time                                                                                                   | Note 16                                                                                              | μs    | _    | 1                    | _    |

<sup>10.</sup> This leakage current is due to an active pull-down NMOS FET at the control input.

<sup>11.</sup> Tested with a 100 pF capacitive load at each output (no current load).

<sup>12.</sup> MACOM MASW-002103 is a 50 MHz to 20 GHz SPDT HMIC Pin Diode Switch. Measured at 10 GHz, 16 dBm, V<sub>CC</sub> = +5 V, V<sub>EEB</sub> = -15 V, and 20 mA forward bias current. The control input was a 0.8 V to 2 V pulse with rise and fall time of 6 ns. 13. When  $V_{CC}$  is below this threshold, the internal power sequencer will pull its output  $V_{SEQ}$  to ground.

<sup>14.</sup> This is the delay between the moment when V<sub>CC</sub> is above the power sequencer threshold to V<sub>SEQ</sub> reaches 90% of steady state value. This is measured with a 47 pF shunt capacitor off  $V_{\text{EEA}}$ .

<sup>15.</sup> This is the time needed for the driver to function properly after V<sub>CC</sub> and V<sub>EEA</sub> reach 90% of their stable value.

<sup>16.</sup> This is the time needed for the internal bias voltages to discharge to 10% of their steady state value after V<sub>CC</sub> and V<sub>EEA</sub> are powered down.

MADR-011034

Rev. V1

### Internal Power Sequencer

For normal operation, negative bias should be applied to  $V_{\text{EEB}}$  (pin 12). The sequencer output  $V_{\text{SEQ}}$  should be connected to the driver die negative bias  $V_{\text{EEA}}$ , with a 47 pF shunt capacitor, as shown in the application schematic next page. The voltage rating of this 47 pF capacitor should be sufficient according to the operating  $V_{\text{EEB}}$ .

When detected  $V_{\text{CC}}$  is above the power sequencer threshold, the negative bias  $V_{\text{EEB}}$  will be passed to the driver. When detected  $V_{\text{CC}}$  is below the power sequencer threshold, the power sequencer will pull  $V_{\text{EEA}}$  to ground to disable the driver.

### **Driving SPDT Switches**

When driving SPDT switches, use C1 and EN as the control inputs. Output A is the non-inverting output, and output B is the inverting output. The unused controls DS and C2 can be left open due to the internal active pull-down. If an all-off RF state is not required, leaving the EN pin open will automatically enable the driver due to the internal active pull-down. The truth table is simplified as follows when DS and C2 are left open:

### **Truth Table for Driving SPDT**

| EN | C1 | Α | В |

|----|----|---|---|

| 1  | Х  | Н | Н |

| 0  | 0  | L | Н |

| 0  | 1  | Н | L |

### **Handling Procedures**

Please observe the following precautions to avoid damage:

### Static Sensitivity

These electronic devices are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these HBM class 1B devices.

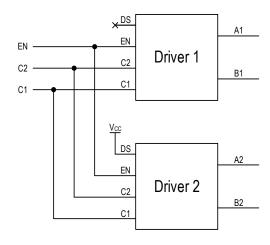

### **Driving SP3T and SP4T Switches**

Two drivers are needed to drive a SP3T or SP4T switch. The DS pin of the first driver can be left open due to the internal active pull-down. Connect the DS pin of the second driver to  $V_{CC}$ . See the figure below for how to connect C1, C2, and EN. The combined truth table is below:

### Truth Table for Driving SP3T and SP4T

| Inputs |    |    | Outputs |    |    |    |

|--------|----|----|---------|----|----|----|

| EN     | C2 | C1 | A1      | B1 | A2 | B2 |

| 1      | Х  | Х  | Н       | Н  | Н  | Н  |

| 0      | 0  | 0  | L       | Н  | Н  | Н  |

| 0      | 0  | 1  | Н       | L  | Н  | Н  |

| 0      | 1  | 0  | Н       | Н  | L  | Н  |

| 0      | 1  | 1  | Н       | Н  | Н  | L  |

MADR-011034 Rev. V1

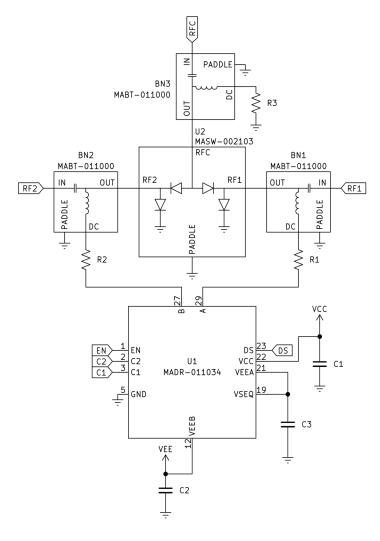

# Application Schematic Driving MASW-002103<sup>17, 18</sup>

## Parts List<sup>18</sup>

| Part          | Value                                   |  |  |

|---------------|-----------------------------------------|--|--|

| U1            | MADR-011034, -10 V to -25 V Driver      |  |  |

| U2            | MASW-002103, HMIC, SPDT Switch          |  |  |

| BN1, BN2, BN3 | MABT-011000, Bias Tee, 2 to 18 GHz      |  |  |

| R1, R2        | Resistor, 0805, 249 Ω, 1%, 1/8 W        |  |  |

| R3            | Resistor, 1206, 453 Ω, 1%, 1/4 W        |  |  |

| C1            | Capacitor, 0805, 16 V, X7R, 10%, 0.1 µF |  |  |

| C2            | Capacitor, 0805, 50 V, X7R, 5%, 0.1 μF  |  |  |

| C3            | Capacitor, 0805, 50 V, X7R, 5%, 47 pF   |  |  |

<sup>17.</sup> If all-off state is not needed, just leave C2, DS, and EN floating and use C1 as the switch control. See the Truth Table for Driving SPDT on the previous page. If all-off state is needed, leave C2 and DS floating, and use C1 and EN as the switch controls.

<sup>18.</sup> The voltage rating of C2 and C3 should be at least two times of V<sub>EE</sub>.

MADR-011034 Rev. V1

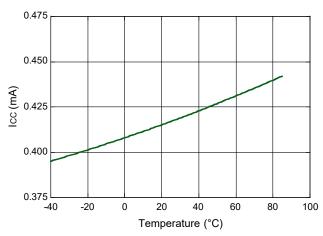

## **Typical Performance Curves**

Quiescent  $I_{CC}$ :  $V_{CC} = +5 V$ ,  $V_{EEB} = -25 V$

### Output Pull-Up On Resistance<sup>19</sup>

Quiescent  $I_{EEB}$ :  $V_{CC}$  = +5 V,  $V_{EEB}$  = -25 V

Output Pull-Down On Resistance<sup>19</sup>

### Control Leakage Current: $V_{CC} = C = +5 V$ , $V_{EEB} = -25 V$

Power Sequencer Threshold:

19. The output on resistance does not change with different V<sub>EEB</sub> voltage levels.

MADR-011034

Rev. V1

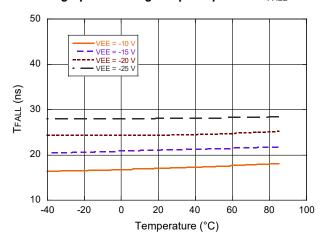

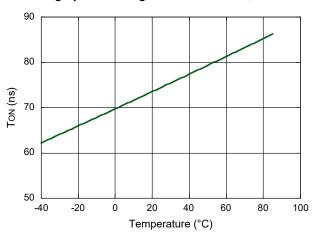

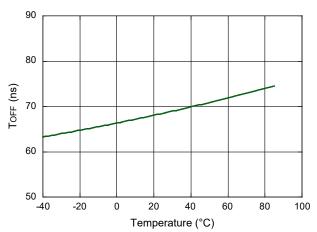

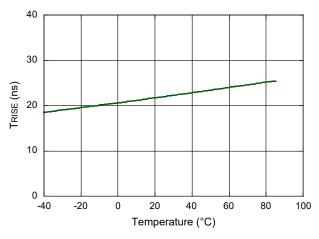

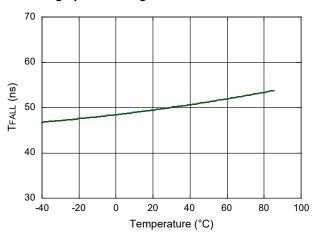

## Typical Performance Curves<sup>20</sup>

### Switching Speed Driving 100 pF Capacitor: Ton

#### Switching Speed Driving 100 pF Capacitor: Toff

#### Switching Speed Driving 100 pF Capacitor: TRISE

#### Switching Speed Driving 100 pF Capacitor: TFALL

20. Tested with a 100 pF capacitor at each output (no current load), V<sub>CC</sub> = +5 V, 0.8 V to 2 V control with rise and fall time of 6 ns.

**MADR-011034**

Rev. V

# Typical Performance Curves<sup>21</sup>

#### Switching Speed Driving MASW-002103: Ton

### Switching Speed Driving MASW-002103: Toff

### Switching Speed Driving MASW-002103: TRISE

#### Switching Speed Driving MASW-002103: TFALL

21. MACOM MASW-002103 is a 50 MHz to 20 GHz SPDT HMIC Pin Diode Switch. Measured at 10 GHz, 16 dBm, V<sub>CC</sub> = +5 V, V<sub>EEB</sub> = -15 V, and 20 mA forward bias current. The control input was a 0.8 V to 2 V pulse with rise and fall time of 6 ns.

MADR-011034 Rev. V1

### Lead-Free 5 mm 32-Lead CQFN<sup>†</sup>

<sup>&</sup>lt;sup>†</sup> Reference Application Note S2083 for lead-free solder reflow recommendations. Meets JEDEC moisture sensitivity level 1 requirements. Plating is Au.

MADR-011034

Rev. V1

### MACOM Technology Solutions Inc. ("MACOM"). All rights reserved.

These materials are provided in connection with MACOM's products as a service to its customers and may be used for informational purposes only. Except as provided in its Terms and Conditions of Sale or any separate agreement, MACOM assumes no liability or responsibility whatsoever, including for (i) errors or omissions in these materials; (ii) failure to update these materials; or (iii) conflicts or incompatibilities arising from future changes to specifications and product descriptions, which MACOM may make at any time, without notice. These materials grant no license, express or implied, to any intellectual property rights.

THESE MATERIALS ARE PROVIDED "AS IS" WITH NO WARRANTY OR LIABILITY, EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MACOM PRODUCTS INCLUDING FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHT, ACCURACY OR COMPLETENESS, OR SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES WHICH MAY RESULT FROM USE OF THESE MATERIALS.

MACOM products are not intended for use in medical, lifesaving or life sustaining applications. MACOM customers using or selling MACOM products for use in such applications do so at their own risk and agree to fully indemnify MACOM for any damages resulting from such improper use or sale.